§2.1. Общие сведения

§ 2.2. Технология изготовления интегральных микросхем

§ 2.3. Гибридные интегральные микросхемы

§ 2.|4. Полупроводниковые интегральные микросхемы

§ 2.5. Параметры интегральных микросхем

§ 2.6. Классификация интегральные микросхем по функциональному назначению и система их обозначений

Общие сведения

Применение электронных устройств для решения все более сложных технических задач приводит к постоянному усложнению их электрических схем. Анализ развития электронной техники показывает, что в течение примерно 10 лет сложность электронных устройств повышается приблизительно в 10 раз. Если в 1975 г. применялись электронные устройства с количеством активных элементов до 10 7 , то в 1985 г. появились устройства с количеством активных элементов около 10 8 . За это же время существенно возросло быстродействие электронных устройств. Так, в 1985 г. большие вычислительные машины элитарного класса достигли быстродействия 100-150 млн. операций в секунду, а вычислительные машины специализированного применения - 5 млрд. операций в секунду.

Существенно снизились габариты полупроводниковых приборов. Размеры одного активного элемента сократились до 1 × 1 × 0,2 мкм, что позволяет размещать в одной микросхеме до 10 6 элементов.

Создание новых электронных устройств с большим количеством элементов стало возможным на базе микроэлектроники. Микроэлектроникой называют новое научно-техническое направление электроники, охватывающее проблемы создания микроминиатюрных электронных устройств, обладающих надежностью, низкой стоимостью, высоким быстродействием и малой потребляемой энергией. Основным конструктивно-техническим принципом микроэлектроники является элементная интеграция - объединение в одном сложном миниатюрном элементе многих простейших элементов (диодов, транзисторов, резисторов и т. д.). Полученный в результате такого объединения сложный микроэлемент называют интегральной микросхемой (ИМС).

Интегральная микросхема - микроэлектронное изделие, содержащее не менее пяти активных элементов (транзисторов, диодов) и пассивных элементов (резисторов, конденсаторов, дросселей), которые изготовляются в едином технологическом процессе, электрически соединены между собой, заключены в общий корпус и представляют неразделимое целое.

С точки зрения интеграции основными параметрами интегральных микросхем являются плотность упаковки и степень интеграции. Плотность упаковки характеризует количество элементов в единице объема интегральной микросхемы, степень интеграции - количество элементов, входящих в состав интегральной микросхемы. По степени интеграции все интегральные микросхемы принято подразделять на ИМС: первой степени интеграции - до 10 элементов, второй степени - от 10 до 100 элементов, третьей степени −от 100 до 1000 элементов и т. д.

Под интегральной схемой (ИС) понимается электронное устройство, имеющее высокую плотность компоновки элементов электрической схемы, в котором все или часть элементов сформированы и электрически соединены между собой на одном полупроводниковом кристалле или диэлектрической подложке.

ИС представляет собой многокомпонентное тело из слоевых композиций на поверхности или в приповерхностном слое твердого тела (полупроводника). Ее характеристики определяются свойствами тонких слоев различных материалов, которые в свою очередь во многом зависят от условий их формирования, последовательности и вида технологических операций.

Вопросы разработки и производства ИС рассматриваются в новой отрасли науки и техники -микроэлектронике, изучающей технологические, физические конструктивные особенности электро- и радиоэлементов с размерами не более 1 мкм хотя бы по одной координате.

Наиболее важной проблемой при создании микросхем является разработка элементов и совместимых друг с другом материалов со стабильными и воспроизводимыми характеристиками тонких слоев, а также последовательности технологических операций формирования многослойной структуры, при которой последующие операции не оказывают вредного влияния на характеристики ранее сформированных слоев.

В зависимости от способа создания пленочных композиций микросхемы делятся на два класса - гибридные интегральные схемы (ГИС) и полупроводниковые интегральные схемы (ИС).

Гибридная интегральная схема - микроминиатюрное электронное устройство, элементы которого нераздельно связаны конструктивно, технологически и электрически на поверхности диэлектрической (стеклянной, керамической) подложки. В технологии ГИС пассивные элементы (резисторы, проводники, контактные площадки, конденсаторы, диэлектрические и изоляционные слои) изготовляют в одном технологическом цикле в виде металлических и диэлектрических пленок на поверхности подложки. Активные компоненты (диоды, транзисторы), а при необходимости также микроминиатюрные дискретные пассивные компоненты (конденсаторы, катушки индуктивности и т. п.) монтируются на поверхности подложки и соединяются с другими элементами.

В зависимости от технологического процесса формирования пассивных элементов гибридные схемы

юдразделяются на тонкопленочные и толстопленочные.

Гонкопленочная технология - последовательное нанесение на общее основание тонких (менее 1-2 мкм) пленочных проводников, контактов, резисторов, изоляторов армированием микрогеометрии элементов и их соединений (топологический рисунок) или в процессе осаждения с помощью трафаретов (масок), а также с помощью вного локального травления сплошных слоев материалов.

Последовательность технологических операций при изготовлении тонкопленочных ГИС по двум вариантам приведена на рис. 19.1.

Толстопленочная технология - последовательное нанесение через сетчатые трафареты и вжигание в керамические подложки паст резистивного, проводящего и диэлектрического назначения.

Проводящие и резистивные пасты представляют собой смесь мелкодисперсного металлического порошка, стекла, выполняющего роль постоянного связующего, и органических жидкостей, обеспечивающих вязкость смеси. Металл обеспечивает образование проводящих (серебро, золото, платина, палладий и их сплавы) или ре-зистивных (благородные металлы и их композиции с оксидами) дорожек.

Пасты для изоляционных слоев представляют собой смесь стекла и органических жидкостей.

Сетчатые трафареты имеют очень малый размер ячеек (порядка 50 мкм). В соответствии с необходимой топологией схемы на некоторых участках трафарета ячейки заполняются эмульсией, пигментной бумагой или фоторезистом, предохраняющими подложку от попадания пасты на эти участки. Нанесение пасты производится перемещающимся ракилем. Вначале наносится проводящая паста для создания соединительных порошков, обкладок конденсаторов, контактных площадок. Паста высушивается, а затем вжигается при температуре 750- 950 °С. Затем через другой трафарет наносится резистивная паста, которая вжигается при меньшей температуре Аналогично наносится и вжигается диэлектрическая паста для образования диэлектрического слоя в толстопленочных конденсаторах и в местах пересечения проводников.

После формирования топологии последовательность других технологических операций аналогична процессам изготовления тонкопленочных схем.

Полупроводниковые (твердотельные) интегральные схемы получают путем целенаправленного локального изменения свойств материала полупроводниковой подложки, легированной примесью.

Добавлением примесей в строго определенных местах и количествах можно изменять проводящие характеристики в материале подложки из полупроводников кремния и германия в очень широком диапазоне - практически от проводника до изолятора. Это свойство используется для получения в кристаллах как активных, так и пассивных элементов. Изменение свойств происходит лишь в небольшом слое кристалла, равном нескольким микрометрам и называемом р-n -переходом, где смыкаются две зоны с различной проводимостью - дырочной и электронной. Остановимся на этом подробно.

Химические элементы кремний и германий имеют на внешней электронной оболочке четыре электрона, т. е. их валентность равна четырем. Известно, что атом имеет более устойчивое состояние, когда на его внешней оболочке находится восемь электронов. При низких температурах в кристаллах полупроводника все электроны связаны с атомами (подвижных электронов нет), и кристалл представляет собой изолятор.

При повышении температуры полупроводника отдельные электроны отрываются от атомов, становятся подвижными и могут создавать электрический ток в кристалле, когда к нему прикладывается напряжение. При удалении электрона из атома в оболочке атома образуется свободное место-дырка. Свободные электроны дырки беспорядочно перемещаются по кристаллу.

При включении такого кристалла в электрическую цепь наблюдается упорядоченное движение электронов от отрицательного полюса к положительному. При стрече свободного электрона с дыркой они рекомбинируют и их движение прекращается. Такая проводимость назыется собственной проводимостью полупроводника.

Если в кристалл кремния или германия ввести небольшое количество, например, алюминия, то проводимость легированного им кристалла будет, в основном, дырочной. Такой кристалл называется полупроводником р-типа.

При введении в кремний и германий, например, мышьяка, получим полупроводник с электронной проводимостью, называемый полупроводником р -типа.

В кристалле полупроводника можно создать с помощью локального легирования одновременно две зоны: p -типа и n -типа. Границу между ними называют р - п- переходом, который может выполнять функции диода.

Создавая разнообразные комбинации р- n -переходов получают элементы - диоды, транзисторы, резисторы и т. п. Сочетания любого числа элементов образуют желаемую схему, а так как все они являются составными частями одного кристалла полупроводникового материала, то получается полностью монолитная твердотельная структура.

Базовой технологией создания полупроводниковых ИС является эпитаксиалъно-планарная технология, по которой поверхность полупроводниковой монокристаллической пластины вначале окисляют. Затем осуществляют локальное травление оксида слоя и через вскрытые в нем окна производят легирование полупроводника. Легирующие примеси диффундируют в подложку из газовой фазы при высокой температуре. Последующим окислением окна снова закрываются. Повторяя технологические операции окисления, селективного травления и диффузии различных примесей, можно реализовать различные схемные элементы: диоды, транзисторы, сопротивления и емкости. Однако емкостные элементы в связи с их большой площадью и высокой стоимостью технологических операций в ИС практически не применяют. На одной пластине монокристалла полупроводника диаметром около 100 мм формируется одновременно до нескольких тысяч ИС.

Последующими операциями технологического процесса являются: получение вакуумным напылением или фотолитографией металлических проводников, которые соединяют элементы схемы, и контактных площадок, отбраковка пластин по параметрам отдельных ИС, разрезка пластины на отдельные ИС, монтаж ИС в корпусе, соединение контактных площадок с выводами корпуса, герметизация.

Выбор конструкции и технологии изготовления интегральных схем обусловливается технико-экономическими соображениями. Толсто- и тонкопленочная технологии отличаются широкими возможностями реализации схем по точности элементов. Кроме того, они характеризуются сравнительно низкой стоимостью подготовки производства. На их базе можно изготовлять широкую номенклатуру схем малых серий (специальных ГИС).

Преимущественное использование тонкопленочной технологии в производстве прецизионных схем объясняется возможностью достижения более высокой разрешающей способности, точности и стабильности элементов схем.

Толстопленочная технология отличается несколько меньшим циклом подготовки производства и менее сложным технологическим оборудованием. Она используется для получения сравнительно несложных схем в устройствах числового программного управления, ЭВМ и др. Для получения ГИС толстопленочная технология в ряде случаев обладает преимуществами по сравнению с тонкопленочной.

Технологию полупроводниковых ИС применяют для изготовления изделий массового производства - цифровых схем ЭВМ, микропроцессоров, электронных часов, счетных машин и т. п.

Ряд технологических операций трех основных видов технологии изготовления интегральных микросхем по своей физической природе аналогичен, несмотря на различия используемых материалов и оборудования.

18 ..Технология изготовления полупроводниковых микросхем

В зависимости от разновидности полупроводниковой технологии (локализация и литография, вакуумное напыление и гальваническое осаждение, эпитаксия, диффузия, легирование и травление) получают области с различной проводимостью, которые эквивалентны емкости, либо активным сопротивлениям, либо различным полупроводниковым приборам. Изменяя концентрацию примесей, можно получить в кристалле многослойную структуру, воспроизводящую заданную электрическую схему.

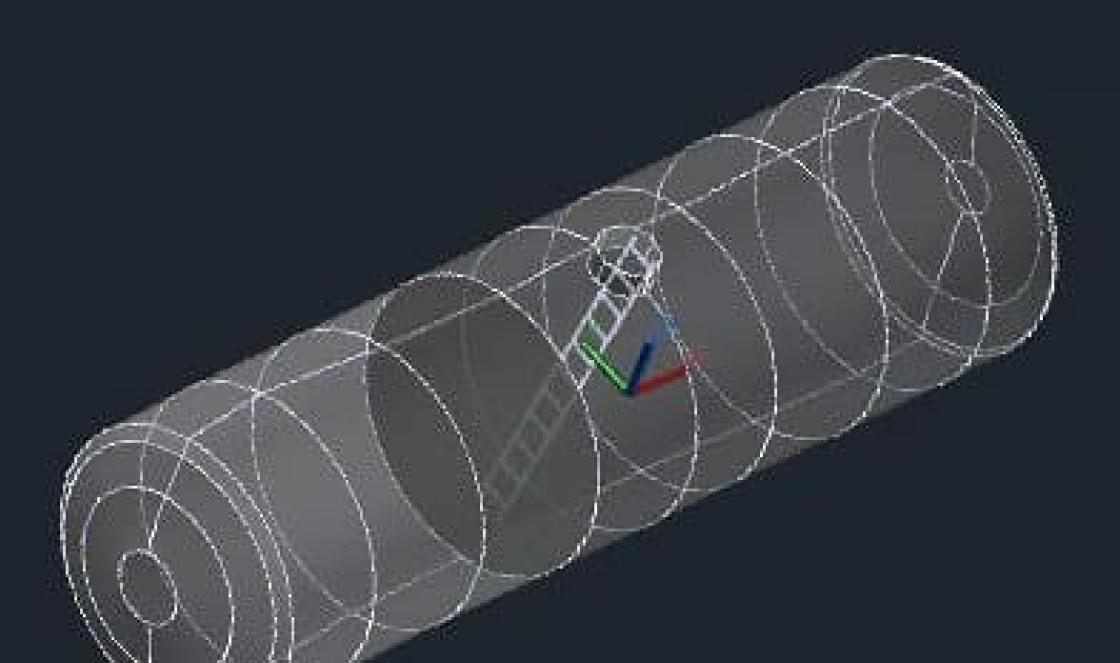

В настоящее время применяют групповые способы изготовления полупроводниковых интегральных микросхем, позволяющие за один технологический цикл получить несколько сотен заготовок микросхем. Наибольшее распространение получил групповой планарный способ, заключающийся в том, что элементы микросхем (конденсаторы, резисторы, диоды и транзисторы) располагаются в одной плоскости или на одной стороне подложки.

Рассмотрим основные технологические процессы, применяемые при изготовлении полупроводниковых микросхем (термическое оксидирование, литография, эпитаксия, диффузия и ионное легирование) .

Рис. 22. Перенос изображений с помощью негативного

(а) и позитивного (б) фоторезистов:

1 -основа фотошаблона, 2 - непрозрачные участки рисунка фотошаблона, 3 -

фоторезистивный слой, 4 - подложка

Термическое оксидирование мало чем отличается от типовых технологических процессов, известных при производстве полупроводниковых приборов. В технологии кремниевых полупроводниковых микросхем оксидные слои служат для изоляции отдельных участков полупроводникового кристалла (элементов, микросхемы) при последующих технологических процессах.

Литография является самым универсальным способом получения изображения элементов микросхемы на кристалле полупроводника и делится на три вида: оптическая, рентгеновская и электронная.

В производстве полупроводниковых интегральных микросхем самый универсальный технологический процесс - это оптическая литография или фотолитография. Сущность процесса фотолитографии основана на использовании фотохимических явлений, происходящих в светочувствительных покрытиях (фоторезистах) при экспонировании их через маску. На рис. 22, а показан процесс негативного, а на рис. 22, б - позитивного переноса изображений с помощью фоторезистов, а на рис. 23 приведена схема технологического процесса фотолитографии.

Весь процесс фотолитографии с помощью фоторезистивной маски состоит из трех основных этапов: формирования на поверхности подложки фото-резистивного слоя 1, фоторезистивной контактной маски II и передачи изображения с фотошаблона на фоторе-зистивный слой III.

Фотолитография может производиться бесконтактным и контактным способами. Бесконтактная фотолитография по сравнению с контактной дает более высокую степень интеграции более высокие требования к фотообо-рудованию.

Процесс получения рисунка микросхемы фотолитографическим способом сопровождается рядом контрольных операций, предусмотренных соответствующими картами технологического контроля.

Рентгеновская литография позволяет получить более высокую разрешающую способность (большую степень интеграции), так как длина волны рентгеновских лучей короче, чем световых. иднако рентгенолитография требует более сложного технологического оборудования.

Электронная литография (электронно-лучевое экспонирование) выполняется в специальных вакуумных установках и позволяют получить высокое качество рисунка микросхемы. Этот вид литографии легко автоматизируется и имеет ряд преимуществ при получении больших интегральных микросхем с большим (более 105) числом элементов.

В настоящее время полупроводниковые элементы и компоненты микросхем получают тремя методами: эпитаксии, термической диффузии и ионного легирования.

Эпитаксия-процесс выращивания слоев с упорядоченной кристаллической структурой путем реализации ориентирующего действия кристалла подложки. Ориентированно выраженные слои нового вещества, закономерно продолжающие кристаллическую решетку подложки, называют эпитаксиальными слоями. Эпитаксиальные слои на кристалле выращивают в вакууме. Процессы эпитаксиального выращивания полупроводниковых слоев аналогичны получению тонких пленок. Эпитаксию можно разделить на следующие этапы: доставка атомов или молекул вещества слоя на поверхность кристалла подложки и миграция их по поверхности; начало группирования частиц вещества около поверхностных центров кристаллизации и образование зародышей слоя; рост отдельных зародышей до их слияния и образования сплошного слоя.

Эпитаксиальные процессы могут быть очень разнообразными. В зависимости от используемого материала (полупроводниковой пластины и легирующих элементов) с помощью процесса эпитаксии можно получить однородные (мало отличающиеся) по химическому составу электронно-дырочные переходы, а также однослойные и многослойные структуры наращивания слоев различных типов проводимости. Этим методом можно получить сложные сочетания: полупроводник - полупроводник; полупроводник -

Диэлектрик; полупроводник - металл.

В настоящее время наиболее широко применяют избирательный локальный эпитаксиальный рост с использованием Si02 - контактных масок с эпитаксиально-планарной технологией.

Для получения заданных параметров эпитаксиальных слоев осуществляют контроль и регулировку толщины, удельного сопротивления, распределения концентрации примеси по толщине слоя и плотности дефектов. Эти параметры слоев определяют пробивные напряжения и обратные токи р-гс-переходов, сопротивления насыщения транзисторов, внутреннее сопротивление и вольт-фа-радные характеристики структур.

Термическая диффузия - это явление направленного перемещения частиц вещества в сторону убывания их концентрации, которое определяется градиентом концентрации.

Термическую диффузию широко используют для введения легирующих примесей в полупроводниковые пластины или в выращенные на них эпитаксиальные слои с целью получения элементов микросхемы противоположного по сравнению с исходным материалом типа проводимости, либо элементов с более низким электрическим сопротивлением. В первом случае получают, например, эмиттеры, во втором- коллекторы.

Диффузию, как правило, проводят в специальных кварцевых ампулах при 1000-1350° С. Способ проведения диффузии и диф-фузант (примесь) выбирают в зависимости от свойств полупроводника и требований, предъявляемых к параметрам диффузионных структур. Процесс диффузии предъявляет высокие требования к оборудованию и частоте легирующих примесей и обеспечивает получение слоев с высокой точностью воспроизведения параметров и толщин. Свойства диффузионных слоев тщательно контролируют, обращая внимание на глубину залегания р-гс-перехода, поверхностное сопротивление или поверхностную концентрацию примеси, распределение концентрации примеси по глубине диффузионного слоя и плотность дефектов диффузионного слоя.

Дефекты диффузионных слоев (эрозию) проверяют с помощью микроскопа с большим увеличением (до 200х) или электрорадиографии.

Ионное легирование также получило широкое применение при изготовлении полупроводниковых приборов с большой плоскостью переходов, солнечных батарей и др.

Процесс ионного легирования определяется начальной кинетической энергией ионов в полупроводнике и выполняется в два этапа. Сначала в полупроводниковую пластину на вакуумной установке с дуговым разрядом внедряют ионы, а затем проводят отжиг при высокой температуре, в результате чего восстанавливается нарушенная структура полупроводника и ионы примеси занимают узлы кристаллической решетки. Метод получения полупроводниковых элементов наиболее перспективен при изготовлении различных СВЧ-структур.

Основные технологические этапы получения полупроводниковых микросхем показаны на рис. 24. Самым распространенным методом получения элементов в микросхеме (разделения участков микросхемы) является изоляция оксидной пленкой, получаемой в результате термообработки поверхности кристалла (подложки).

Чтобы получить изолирующие р-гс-переходы на подложке кремниевой пластины 1, ее обрабатывают в течение нескольких часов в окислительной среде при 1000-1200° С. Под действием окислителя эпитаксиальный полупроводниковый поверхностный слой кремния 2 окисляется. Толщина оксидной пленки 3 - несколько десятых долей микрона. Эта пленка препятствует проникновению в глубь кристалла атомов другого вещества. Но если снять пленку с поверхности кристалла в определенных местах, то с помощью диффузии или других рассмотренных выше методов можно ввести в эпитаксиальный слой кремния примеси, создав тем самым участки различной проводимости. После того как на подложке получена оксидная пленка, на подложку наносят светочувствительный слой - фоторезист 4. Далее этот слой используют для получения в нем рисунка фотошаблона 5 в соответствии с топологией микросхемы.

Перенос изображения с фотошаблона на окисленную поверхность кремниевой пластины, покрытую слоем фоторезиста, чаще всего производят фотографией, а экспонирование - ультрафиолетовым светом или рентгеном. Затем подложку с экспонированным рисунком проявляют. Те участки, которые освещались, растворяются в кислоте, обнажая поверхность оксида кремния 6. Те же участки, которые не экспонировались, кристаллизуются и становятся нерастворимыми участками 7. Полученную подложку с нанесенной на ней рельефной схемой расположения изолирующих переходов промывают и сушат. После травления незащищенных участков оксида кремния защитный слой фоторезиста удаляют химическим способом. Таким образом, на подложке получают «окна». Такой способ получения рисунка схемы называют позитивным.

Рис. 24. Основные технологические этапы получения полупроводниковых микросхем

Через обнаженные участки 6 подложки методом диффузии вводят примеси атомов бора или фосфора, которые создают изолирующий барьер 8. На полученных изолированных друг от друга участках подложки методом вторичной диффузии, травления, наращивания или другим методом получают активные и пассивные элементы схемы и токопроводящие пленки 9.

Технология получения полупроводниковых интегральных схем состоит из

15-20, а иногда и более операций. После того как

получены все компоненты схем и пленка оксида вытравлена с тех мест, где

будут находиться выводы компонентов, полупроводниковую схему покрывают

методом напыления или гальванического осаждения пленкой алюминия. С

помощью фотолитографии с последующим травлением получают внутрисхемные

соединения.

Поскольку в едином технологическом цикле на подложке изготовляют большое количество однотипных интегральных схем, пластины разрезают на отдельные кристаллы, каждый из которых содержит готовую микросхему. Кристаллы приклеивают к держателю корпуса, а электрические контакты микросхемы методом пайки, сварки и термокомпрессии соединяют с выводами проволочными перемычками. Готовые микросхемы при необходимости герметизируют одним из описанных ниже способов.

Промышленность выпускает большую номенклатуру полупроводниковых интегральных микросхем. Например, кремниевые микросхемы с диодно-транзисторными связями предназначены для работы в логических узлах ЭВМ и узлах автоматики; германиевые полупроводниковые микросхемы с непосредственными связями являются универсальными логическими переключающими элементами НЕ - ИЛИ.

Дальнейшим развитием технологии производства интегральных микросхем явилось создание схем с большой интеграцией микроэлементов.

В совмещенной интегральной микросхеме элементы выполнены в объеме и на поверхности полупроводниковой подложки комбинированием технологии изготовления полупроводниковых и пленочных микросхем. В монокристалле кремния - подложке методами диффузии, травления и другими получают все активные элементы (диоды, транзисторы и др.), а затем на эту подложку, покрытую плотной пленкой оксида кремния, напыляют пассивные элементы (резисторы, конденсаторы) и токопроводящие проводники. Совмещенную технологию применяют для изготовления микро-мощных и быстродействующих интегральных микросхем.

Для получения контактных площадок и выводов микросхемы на подложку осаждают слой алюминия. Подложка со схемой крепится на внутреннем основании корпуса, контактные площадки на монокристалле соединяются проводниками с выводами корпуса микросхемы.

Совмещенные интегральные микросхемы конструктивно могут быть выполнены в виде моноблока довольно малых размеров. Например, двухкаскадный высокочастотный усилитель, состоящий из двух транзисторов и шести пассивных элементов, размещается на монокристалле кремния размером 2,54X1,27 мм.

Быстрый рост интеграции полупроводниковых микросхем при разработке РЭА привел к созданию микросхем высокой степени сложности: БИС, СБИС и БГИС (микросборок).

Большая интегральная схема представляет собой сложную полупроводниковую

микросхему с высокой степенью интеграций. В последние годы созданы

полупроводниковые БИС, имеющие

на кристалле кремния размером 1,45x1,6 мм до 1000 и более элементов

(транзисторов, диодов, резисторов и др.) и выполняющие функции 300 и

более отдельных интегральных микросхем. Разработан микропроцессор

(микро-ЭВМ), имеющий степень интеграции свыше 107 элементов на

кристалле.

Используя несколько навесных структур БИС на диэлектрической подложке с пассивной пленочной частью микросхем, можно получить микросборки (БГИС), которые просты в проектировании и изготовлении.

Повышение интеграции микросхем достигается автоматизацией и введением в технологический процесс математического моделирования с машинным проектированием топологии и применением новых методов формирования элементов микросхем (ионное легирование и др.).

Основной цикл проектирования БИС состоит из двух этапов: архитектурно - схемотехнического и конструкторско - технологического.

Архитектурно-схемотехнический этап включает разработку архитектуры и структуры микросхемы, функциональных и принципиальных электрических схем, математическое моделирование и другие работы.

Конструкторско-технологический этап включает разработку топологии и конструкции микросхемы, технологии ее изготовления, а также их испытания.

Большие и сверхбольшие интегральные микросхемы на современном уровне представляют последний этап развития классических интегральных микросхем, в которых можно выделить области, эквивалентные пассивным и активным элементам. Дальнейшее развитие элементной базы электроники возможно при использовании различных эффектов и физических явлений в молекулах твердого тела (молекулярная электроника).

Знаете ли Вы, в чем ложность понятия "физический вакуум"?

Физический вакуум - понятие релятивистской квантовой физики, под ним там понимают низшее (основное) энергетическое состояние квантованного поля, обладающее нулевыми импульсом, моментом импульса и другими квантовыми числами. Физическим вакуумом релятивистские теоретики называют полностью лишённое вещества пространство, заполненное неизмеряемым, а значит, лишь воображаемым полем. Такое состояние по мнению релятивистов не является абсолютной пустотой, но пространством, заполненным некими фантомными (виртуальными) частицами. Релятивистская квантовая теория поля утверждает, что, в согласии с принципом неопределённости Гейзенберга, в физическом вакууме постоянно рождаются и исчезают виртуальные, то есть кажущиеся (кому кажущиеся?), частицы: происходят так называемые нулевые колебания полей. Виртуальные частицы физического вакуума, а следовательно, он сам, по определению не имеют системы отсчета, так как в противном случае нарушался бы принцип относительности Эйнштейна, на котором основывается теория относительности (то есть стала бы возможной абсолютная система измерения с отсчетом от частиц физического вакуума, что в свою очередь однозначно опровергло бы принцип относительности, на котором постороена СТО). Таким образом, физический вакуум и его частицы не есть элементы физического мира, но лишь элементы теории относительности, которые существуют не в реальном мире, но лишь в релятивистских формулах, нарушая при этом принцип причинности (возникают и исчезают беспричинно), принцип объективности (виртуальные частицы можно считать в зависимсоти от желания теоретика либо существующими, либо не существующими), принцип фактической измеримости (не наблюдаемы, не имеют своей ИСО).

Когда тот или иной физик использует понятие "физический вакуум", он либо не понимает абсурдности этого термина, либо лукавит, являясь скрытым или явным приверженцем релятивистской идеологии.

Понять абсурдность этого понятия легче всего обратившись к истокам его возникновения. Рождено оно было Полем Дираком в 1930-х, когда стало ясно, что отрицание эфира в чистом виде, как это делал великий математик, но посредственный физик , уже нельзя. Слишком много фактов противоречит этому.

Для защиты релятивизма Поль Дирак ввел афизическое и алогичное понятие отрицательной энергии, а затем и существование "моря" двух компенсирующих друг друга энергий в вакууме - положительной и отрицательной, а также "моря" компенсирующих друг друга частиц - виртуальных (то есть кажущихся) электронов и позитронов в вакууме.

на тему: «Технология изготовления кристаллов полупроводниковых интегральных микросхем »

Дисциплина: «Материаловедение и материалы электронных средств»

Выполнил студент группы 31-Р

Козлов А. Н.

Руководитель Косчинская Е. В.

Орел, 2004

Введение

Часть I. Аналитический обзор

1.1 Интегральные схемы

1.3 Характеристика монокристаллического кремния

1.4 Обоснование применения монокристаллического кремния

1.5 Технология получения монокристаллического кремния

1.5.1 Получение кремния полупроводниковой чистоты

1.5.2 Выращивание монокристаллов

1.6 Механическая обработка монокристаллического кремния

1.6.1 Калибровка

1.6.2 Ориентация

1.6.3 Резка

1.6.4 Шлифовка и полировка

1.6.5 Химическое травление полупроводниковых пластин и подложек

1.7 Операция разделения подложек на платы

1.7.1 Алмазное скрайбирование

1.7.2 Лазерное скрайбирование

1.8 Разламывание пластин на кристаллы

Часть II. Расчет

Заключение

Список используемой литературы

Технология изготовления интегральных микросхем представляет собой совокупность механических, физических, химических способов обработки различных материалов (полупроводников, диэлектриков, металлов), в результате которой создается ИС.

Повышение производительности труда обусловлено в первую очередь совершенствованием технологии, внедрением прогрессивных технологических методов, стандартизацией технологического оборудования и оснастки, механизацией ручного труда на основе автоматизации технологических процессов. Значимость технологии в производстве полупроводниковых приборов и ИС особенно велика. Именно постоянное совершенствование технологии полупроводниковых приборов привело на определенном этапе ее развития к созданию ИС, а в дальнейшем - к широкому их производству.

Производство ИС началось примерно с 1959 г. На основе предложенной к этому времени планарной технологии. Основой планарной технологии послужила разработка нескольких фундаментальных технологических методов. Наряду с разработкой технологических методов развитие ИС включало исследования принципов работы их элементов, изобретение новых элементов, совершенствование методов очистки полупроводниковых материалов, проведение их физико-химических исследований с целью установления таких важнейших характеристик, как предельные растворимости примесей, коэффициенты диффузии донорных и акцепторных примесей и др.

За короткий исторический срок современная микроэлектроника стала одним из важнейших направлений научно-технического прогресса. Создание больших и сверхбольших интегральных микросхем, микропроцессоров и микропроцессорных систем позволило организовать массовое производство электронных вычислительных машин высокого быстродействия, различных видов электронной аппаратуры, аппаратуры управления технологическими процессами, систем связи, систем и устройств автоматического управления и регулирования.

Микроэлектроника продолжает развиваться быстрыми темпами, как в направлении совершенствования полупроводниковой интегральной технологии, так и в направлении использования новых физических явлений.

Часть I . Аналитический обзор

1.1 Интегральные схемы

В процессе развития микроэлектроники (МЭ) номенклатура ИС непрерывно изменялась. Главный тип ИС в настоящее время - полупроводниковые ИС.

Классификация ИС.

Классификация ИС может производиться по различным признакам, ограничимся одним. По способу изготовления и получаемой при этом структуре различают два принципиально разных типа интегральных схем: полупроводниковые и пленочные.

Полупроводниковая ИС - это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки. Эти ИС составляют основу современной микроэлектроники.

Пленочная ИС - это микросхема, элементы которой выполнены в виде разного рода пленок, нанесенных на поверхность диэлектрической подложки. В зависимости от способа нанесения пленок и связанной с этим их толщиной различают тонкопленочные ИС (толщина пленок до 1-2 мкм) и толстопленочные ИС (толщина пленок от 10-20 мкм и выше).

Поскольку до сих пор никакая комбинация напыленных пленок не позволяет получить активные элементы типа транзисторов, пленочные ИС содержат только пассивные элементы (резисторы, конденсаторы и т. п.). Поэтому функции, выполняемые чисто пленочными ИС, крайне ограничены. Чтобы преодолеть эти ограничения, пленочную ИС дополняют активными компонентами (отдельными транзисторами или ИС), располагая их на той же подложке и соединяя с пленочными элементами. Тогда получается ИС, которую называют гибридной.

Гибридной ИС (или ГИС) - это микросхема, которая представляет собой комбинацию пленочных пассивных элементов и активных компонентов, расположенных на общей диэлектрической подложке. Дискретные компоненты, входящие в состав гибридной ИС, называются навесными, подчеркивая этим их, обособленность от основного технологического цикла получения пленочной части схемы.

Еще один тип «смешанных» ИС, в которых сочетаются полупроводниковые и пленочные интегральные элементы, называют совмещенными.

Совмещенная ИС - это микросхема, у которой активные элементы выполнены в приповерхностном слое полупроводникового кристалла (как у полупроводниковой ИС), а пассивные нанесены в виде пленок на предварительно изолированную поверхность того же кристалла (как у пленочной ИС).

Совмещенные ИС выгодны тогда, когда необходимы высокие номиналы и высокая стабильность сопротивлений и емкостей; эти требования легче обеспечить с помощью пленочных элементов, чем с помощью полупроводниковых.

Во всех типах ИС межсоединения элементов осуществляются с помощью тонких металлических полосок, напыленных или нанесенных на поверхность подложки и в нужных местах контактирующих с соединяемыми элементами. Процесс нанесения этих соединительных полосок называют металлизацией, а сам «рисунок» межсоединений - металлической разводкой.

В данной курсовой работе рассмотрена технология изготовления плат полупроводниковых интегральных микросхем. Полупроводниковая интегральная микросхема – это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки. Эти ИС составляют основу современной микроэлектроники. Размеры кристаллов у современных полупроводниковых интегральных микросхем достигают 20x20 мм, чем больше площадь кристалла, тем более многоэлементную ИС можно на ней разместить. При одной и той же площади кристалла можно увеличить количество элементов, уменьшая их размеры и расстояния между ними.

1.2 Требования к полупроводниковым подложкам

Полупроводники в виде пластин или дисков, вырезанных из монокристаллов, называются подложками. В их объеме и на поверхности методами травления, окисления, диффузии, эпитаксии, имплантации, фотолитографии, другими технологическими приемами формируются элементы микросхем электронных приборов и устройств.

Качество поверхности подложки определяется ее микрорельефом (шероховатостью), кристаллическим совершенством поверхностных слоев и степенью их физико-химической чистоты. Поверхность подложки характеризуется неплоскостностью и непараллельностью. Высокие требования предъявляются и к обратной - нерабочей стороне подложки. Неодинаковая и неравноценная обработка обеих сторон подложки приводит к дополнительным остаточным механическим напряжениям и деформации кристалла, что обусловливает изгиб пластин.

После механической обработки в тонком приповерхностном слое подложки возникает нарушенный слой. По глубине он может быть разделен на характерные зоны. Для кристаллов Ge, Si, GaAs и других после их резки и шлифования на глубине 0,3...0,5 средней высоты неровностей расположена рельефная зона, в которой наблюдаются одинаковые виды нарушений и дефектов монокристаллической структуры: монокристаллические сколы, невыкрошившиеся блоки, трещины, выступы и впадины различных размеров. После резки дефекты располагаются в основном под следами от режущей кромки алмазного диска в виде параллельных дорожек из скоплений дефектов, в шлифованных кристаллах - равномерно по сечению. При полировании первый слой представляет собой поверхностные неровности, относительно меньшие, чем при шлифовании, и в отличие от шлифованной поверхности он является аморфным. Второй слой также аморфный, его глубина в 2...3 раза больше, чем поверхностные неровности. Третий слой является переходным от аморфной структуры к ненарушенному монокристаллу и может содержать упругие или пластические деформации, дислокации, а в некоторых случаях и трещины. В процессе обработки и подготовки поверхности подложек полупроводников необходимо создание совершенных поверхностей, имеющих высокую степень плоскопараллельности при заданной кристаллографической ориентации, с полным отсутствием нарушенного слоя, минимальной плотностью поверхностных дефектов, дислокаций и т.д. Поверхностные загрязнения должны быть минимальными.

3 Характеристика монокристаллического кремния

Физико-химические свойства кремния

1.Оптимальное значение ширины запрещенной зоны, которая обусловила достаточно низкую концентрацию собственных носителей и высокую рабочую температуру.

2.Большой диапазон реально достижимых удельных сопротивлений в пределах от 10 -3 Ом-см (вырожденный) до 10 5 (близкий к собственному).

3.Высокое значение модуля упругости, значительная жесткость (большая, чем, например, у стали).